# Optimized Centralized Network Selection in Heterogeneous Wireless Network

Gurumurthy G D, Research Scholar, Mewar university, Rajasthan, India, gurumurthygd@gmail.com Dr. H S Shivaram, Research Supervisor, Mewar University, Rajasthan, India, hs.shivaram@gmail.com

*Abstract* - Seamless continuity of service and to stay always best connected will be the feature of next generation wireless communication networks. Wireless networks which are of different radio access technology and having different characteristic such as Wi-Fi, UMTS, Wi-MAX, LTE etc.. coexist forming a heterogeneous wireless network. Mobile nodes (MN) which have multiple radio access interfaces can interoperate in heterogeneous networks by initiating vertical handoff, to achieve seamless continuity of service. Achieving vertical handoff in heterogeneous networks is facilitated by IEEE802.21 media independent specifications. In the regions covered by overlaid heterogeneous wireless networks mobile nodes can make vertical handover to the best network for want of quality of service thus achieving always best connected. Selecting an appropriate radio access technology as a candidate network to handover is critical issue. Vertical handover algorithms consider various network parameters such as RSS, Band width, average delay, security etc as metrics to estimate the quality of service(qos) provided by different networks . Vertical handover algorithms are designed based on different mathematical methods to select appropriate candidate network. To achieve optimization in handover process quick decision of suitable candidate network selection process.

Keywords - Heterogeneous wireless network, vertical handoff, candidate network, Access point, Mobile Node ,MIIS server, qos

# I. INTRODUCTION

The extensive use of mobile communication by the users has revolutionized the growth of mobile networks. In many regions different networks are simultaneously available .These networks may be of different type and of different radio access technology. A large geographical area is covered by mobile network facility by one or another network type. If the mobile devices possess the capacity to access these different network types and the networks are suitably linked to provide interoperability for mobile nodes such networks are referred to as heterogeneous networks. The heterogeneous networks opened up the scope for always connected to mobile users.

The heterogeneous networks of different type which differ in the characteristic as signal strength, bandwidth, coverage area, delay etc.. co exists and are overlaid and simultaneously available to the users. These overplayed networks make the possibility of always best connected to users. The networks such as Wi-Fi have small coverage area and large bandwidth ,UMTS network have large coverage area at lower bandwidth [1]. The existence of overlaid heterogeneous networks in a location make provision for the wireless network users to stay connected to best network among the simultaneously available different radio access technologies. To harness the benefit of heterogeneity the mobile devices should posses the capacity to access these networks on a single mobile node. The mobile nodes which have multiple interfaces to interact with different radio access technologies are referred to as multimode nodes. The multimode terminals can interoperate in a heterogeneous network by vertical handover mechanism. Vertical handover is a process of continuation of ongoing session by hand over from one radio access technology to another network of different radio access technology, by the usage of multimode mobile devices [2]

The handover process in homogeneous network take place by considering a single parameter mainly RSS. In heterogeneous environment different networks have different characteristic handover based on single parameter do not provide quality of service [3], To ensure qos in handover operation following issues are to be given attention. (i)Maintaining seamless connectivity (ii) Selection the most suitable candidate network to handover (iii) choosing the right time to initiate handover. The handover management in heterogeneous environment involve the following phases.(i) Deciding the necessity to handover (ii) Gathering the information about neighboring networks and access points (iii) selection of appropriate candidate network to handover (iv)To decide to handover and execute handover.

To facilitate vertical handover IEEE802.21 Media Independent Handover (MIH) standard has specified three typed of services

# Low Cost Data Acquisition System for ECG

Rudresh M D Research Scholar, KIT, Tiptur Karnataka, India-572201 H S Jayanna, PhD SIT, Tumkur Karnataka, India-572103 Anitha sheela K, PhD JNTUH, Hyderabad Telangana, India

# ABSTRACT

The objective of this research work is to develop a low cost circuitry for Electrocardiogram (ECG) data acquisition system that outputs optimum ECG data with very low noise and minute spectral information loss. The experimental results demonstrate that by the careful choice electrodes and placement of electrodes, it is indeed possible to collect pure ECG signal. By using this system, acquires the filtered and amplified ECG data through Line-In port of sound card of computer through MATLAB software. In the design of ECG data acquisition used the instrumentation amplifier packed IC module instead of separate opamp module which results in high common mode rejection ratio up to 80db and minimizes the offset voltage, to very low value up to 25µV and in the design of the notch filter circuits uses UAF42IC, and in the design circuitry of low pass, high pass filter uses the opamp TLO84ICs. The ECG data recorded by developed system useful for purposes of diagnosis of heart related diseases and also researchers study purposes.

#### **Keywords**

Electrocardiogram, LABVIEW, Notch Filter, CMRR

#### **1. INTRODUCTION**

Electrocardiogram (ECG) signals plays a vital role in clinical diagnosis especially for diagnosing heart related diseases and disorders such as, cardiovascular disease (CVD), pulmonary disease, sudden cardiac arrest (SCA), etc [1]. ECG signal is generated by a nerve impulse stimulus to a heart. The current is diffused around the surface of the body and build on the voltage drop, which is a normally 0.0001 to 0.003volt and the signals are within the frequency range of 0.05 to 100 Hz [1] [2]. ECG signals are usually recorded at the surface of the body and processed to give important information about the electrical activity of heart.

A typical ECG tracing of a normal heartbeat consists of a P wave, a QRS complex and a T wave. Usually, the signal which is acquired from the human body is of very low potential and difficult to analyze the signal variance. Hence, necessary amplification is required before processing the ECG signal to derive any give useful information about the cardiac abnormalities. The elements of ECG complex Zeli Gao et.al, developed an 2 lead ECG device with lead I configuration, Right Leg driven circuit and used total gain of 1000. The active filter is used to obtain ECG signal with a frequency range of 0.05 Hz to 150 Hz and used NI USB 6008DAQ card to integrate with LAB VIEW [3].

In [4], the researchers have developed a lead II ECG data acquisition device with a cut off frequency of low pass and notch filter with a value of 150 Hz and 60 Hz, respectively. They used ADuC831 DAQ system to be integrated to J Free Chart for ECG data acquisition. Steve et. al used lead II configuration with a gain of 987[5]. These researchers acquired ECG signal with a frequency range of 0.1-50Hz and implemented inverting amplifier before hardware integration

to my DAQ to be read by LABVIEW software [5]. Above mentioned literature works, motivated us to develop low cost ECG data acquisition.

Based on the literature, this paper research work consists of several stages such as, pre-amplification, isolation, filtering and second stage of amplification to acquire the ECG signals using three ECG leads [6-7]. In general, multi-stage amplifiers are required to amplify the ECG signals with a larger gain. Meanwhile, the amplifiers should have a high common-mode rejection ratio (CMRR) to amplify the ECG signal. This amplifier usually amplifies the most useful information of heart activities along with inherent noises developed in a system during data acquisition. These noises are filtered using both high and low pass filters, to extract the ECG signal between 0.05 Hz and 113 Hz.

To develop data acquisition system we employed an instrumentation amplifier to reject common mode signals and optimize its CMRR using resistance tuning and matching. A single order high pass filter of 10 Hz is used in the feedback of Instrumentation Amplifier output stage to prevent the saturation of data due to Base line noise and motion Artifact. Then to remove other noise such as ECG and other biomedical signal interference, 6th order unity gain chebyshev Active high pass filter(Sallen-Key Architecture) and to remove thermal noise a 4th order Butterworth active low pass filter is employed. To overcome the problem with non-ideal operation of op-amps at high frequency one single order passive low pass RC filter is also employed. To remove line frequency components a new approach is used than the conventional notch filter as twin-t filter and Inductor Simulated Notch Filter. After design and development of acquisition system, we acquire the filtered and amplified ECG data through Line-in port of sound card of computer using MATLAB software.

Our study is organized as follows: Section 1 is the introduction, Section 2 describes the block diagram of single channel ECG signal acquisition system, Section 3 presents experimental results and discussion and Finally, the conclusion is made in Section 4.

# 2. DEVELOPMENT OF ECG SIGNAL ACQUISITION SYSTEM

A detailed study of physiological origin of ECG signal, thorough study of characteristics of ECG signal, amplitude, time and frequency domain properties of ECG signal and sources of noise during its acquisition provided us insight into the complex nature of ECG signal. The use of surface electrodes for measuring the action potentials accompanying muscle contraction requires high-gain amplifiers having flat frequency response and high input impedance. The amplitude of ECG signal varies from few micro volts to few mill volts. The usable energy of signal is limited to 2 Hz to 100 Hz frequency range, with dominant energy being 10 to 60 Hz range [4]. The amplitude, time and frequency domain

Nayana C G et al. International Journal of Engineering, Basic sciences, Management & Social studies Volume 1, Issue 1, May 2017 Special Issue on "Emerging Trends in Electronics and Communication Engineering" 4th National Conference NCETEC-2017, Organized by Department of ECE, BGS Institute of Technology, BG Nagara, Mandya, Karnataka, India

# SURVEY ON CARRYING DIGITAL IMAGE WATERMARKING IN HEALTHCARE BASED MEDICAL PALMISTRY

Nayana C G<sup>1</sup>, <sup>1</sup>Assistant Professor, Department of TCE, GSSSIETW, Mysuru, Karnataka, India

Shruthi S Prabhu<sup>2</sup>

,<sup>2</sup>Assistant Professor, Department of TCE, GSSSIETW, Mysuru, Karnataka, India Dr.Parameshachari B

<sup>3</sup>Professor and Head , Department of TCE, GSSSIETW, Mysuru, Karnataka, India

<sup>3</sup>,Rudresh M D<sup>4</sup>

<sup>4</sup>Associate Professor , Department of TCE, KIT, Tiptur, Karnataka, India

## ABSTRACT

In this paper, an application of digital image processing is discussed which can be useful in healthcare domain to predict some major diseases based on certain palm features called medical palmistry. The application is an image processing system, the images of human palm form input to the system. Then, system applies digital image processing and analysis techniques on input images to identify certain features in the image. By using knowledge base of medical palmistry it analyzes certain features in image and predicts probable disease. In case of telemedine the recorded palmistry data is required to send in electronic format, which is called electronic patient records (EPRs). These records can be made available over the internet, which provides effective healthcare for the patients. But information security and privacy is one of the major issue due to advancement in wireless technologies. EPRs contain sensitive information which should not be accessed by unauthorized persons. Cryptography and steganography provide certain solution to the security and privacy issues, digital watermarking is proved to be the best technique for image security, integrity and confidentiality. At the same time it will provide authenticity of patients.

Keywords— Electronic Patient Records (EPRs), Image Processing and Analysis (IPAA), Region of Interest(ROI).

## I. INTRODUCTION

An image may be defined as a two-dimensional function, f(x,y), where x and y are spatial (plane) coordinates, and the amplitude of f at any pair of coordinates (x,y) is called the intensity or grey level of the image at that point. When x, y and the amplitude values of f are infinite, we call the image an analog image. When these values are finite, discrete quantities, we call the image a digital image [6]. The field of digital image processing refers to processing digital images by means of a digital computer. Once computer has visual information in appropriate format, computer can analyze it, which is called image analysis. Image understanding and analysis is difficult task. In healthcare industry, there are so many applications of digital image processing. Medical Pamistry, Magnetic Resonance Imaging (MRI) and Computerized Tomography (CT) scan are most popular among them. Apart of healthcare, Digital Image Processing and analysis is also applied in different areas like office and industrial automation, Remote sensing; natural resources survey and management, Criminology, Astronomy, Meteorology, and artillery applications.

Telemedicine is enabling medical health records to be in the electronic format, which is called electronic patient's records, EPRs, and making them available to the users via the Internet. It provides cheap and effective healthcare to rural patients. However, information privacy and security issues telemedicine projects,

# High-Speed and Energy-Efficient Carry Skip Adder functioning under a extensive range of supply voltage Levels

Amrutavarshini S H, Mr. S Pramod Kumar

Amrutavarshini S H,PG student/ VLSI and ES, ECE, Kalpataru Institute of Technology Tiptur, Tumkur, India Asst. Prof, S Pramod Kumar ECE Department, Kalpataru Institute of Technology Tiptur, Tumkur, India

#### Abstract—

In this paper, we herein present a structure of adder which has higher speed yet lower energy at consumption which when compared with the conventional one. The speed of the enhancement is achieved by applying the concatenation and the scheme of incrementation to ameliorate the efficiency of the conventional CSKA structure. Instead premeditating on the multiplexer logic, suggested structure makes utilization of AND-OR-Invert or AOI and OR-AND-Invert compound gates for those skip logic. The whole structure may be realized with both fixed stage size and also variable style in size wherein the latter furthering augments the speed and the respective parameters of energy of the corresponding adder. Ultimately, hybrid variable latency at extension of the suggested structure, which lessens the utilization of the power without making an impact at the speed which is representing a speed. This extension utilizes the amended parallel type structure basically for augmenting the feeble time thus capacitating at the further reduction of voltage. Suggested structure are assessed by making a comparison of their speed, power and parameters of energy with those of other type adders utilizing a forty nm static CMOS in technology for an extensive range of supply of voltage.

#### **III CHANGE IN VOLTAGE**

In these circuits, we herein reduce the consumption of energy and system may amend the voltage and those of frequency of the considered which is relied on the requirement of the workload. For these systems, the circuit need be able to operate under extensive range of supply of levels of voltages.

#### IV OPTIMISING POWER AND SPEED

In considering addition of the knob of the respective supply of voltage, one may chose between the different structures of adder or families primarily for optimizing at the power and the speed. Fewer speed of this considered structured adder of CSLA and the PPA, however does limits its utilization for the high speed applications.

#### V STRUCTURAL ADJUSTMENT

Adjustment of the structure is reckoned on the technique of variable latency which in turn does lowers the consumption of power without which **Key words:** Carry skip adder(CSKA), Ripple Carry adder(RCA)

### **I INTRODUCTION**

Depending on the quantity of the supply voltage reduction, the functioning of the ON devices does reside in the threshold, near threshold or even subthreshold regions. Working at the super threshold region does provides us with the lower delay and even greater switching and leakage of powers can be compared with the near or threshold regions. In the subthreshold region, logic gate in lagging and the respective leakage power does exhibit the exponential reliance's on those of supply and the voltages.

#### **II MOTIVATION**

The reckoning of the power on the supply of voltage has been the motivation for the design of those circuits with the feature of dynamic voltage and the scaling.

considerably makes an impact those of CSKA speed which is presented. Suggested amendments do ameliorates the respective speed.

#### VI WORKING WITH AMALGAMATION

Amended CSKA structure considered amalgamating the concatenation and those of schemes of incrementation to the conventional CSKA for embellishing the speed and energy capacitance of the adder. This amendments does offers with the ability to utilize simpler carry skip logics which is based on the AOI/OAI compound gates instead of the multiplexer.

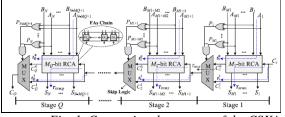

Fig. 1. Conventional structure of the CSKA

# Novel Transform Domain Techniques for Person Identification using ECG Signals

Rudresh M. D.

Research Scholar, JNTU, Hyderabad Kalpataru Institute of Technology Tiptur, Karnataka, India H. S. Jayanna

Professor, Dept. of ISE Siddaganga Institute of Technology Tumkur, Karnataka, India Anitha Sheela K. Professor, Dept. of ECE JNTU, Hyderabad Telangana State, India

# ABSTRACT

The person identification is an active area in research fields. many person identification techniques have been proposed in literature both in time domain and transformed domain. An improved various transformed domain techniques are proposed in this paper. This paper work also demonstrates the task of identifying the person with the various segments of ECG signals, and also investigates which segments of ECG signals has more person specific information by using transformational methods. A transformed domain technique includes discrete fourier transform, discrete cosine transform and discrete wavelet transform. An experimental results on ECG signals using transformed domain techniques demonstrates that the improvement of proposed techniques over those of time domain techniques.

## **Keywords**

ECG person identification, CCORR, PRD, Wavlet distance measure.

# 1. INTRODUCTION

In today's world, we can see the application of person recognition in many places starting from commercial applications, such as internet access, ATM, credit card, cellular phone, to the government and forensic applications like driver's license, pass-port control and criminal investigation, terrorist identification etc, The main purpose of of person identification system is to ensure that the rendered services are accessed only by a legitimate user and no one else, i.e., to confirm or determine the identity of an individual requesting for service.

Traditional password-based and other identification systems have a number of flaws. A password can be forgotten or elicited, and such systems are easy to hack. One needs to always carry the identification key around, which is inconvenient. there are chances that the intruder can get hold of your password. Besides, a person cannot be identified without any specific physical carrier. Together, all those factors prompt us to look for new approaches to the problem. Biometrics techniques truly identifies the actual applicant as a particular individual than other traditional methods like photo identity card, tokens, badges and passwords etc which may be hacked by somebody. Biometrics provides an automatic method of recognizing a person based upon intrinsic physical or behavioral features, such as face, voice, retinal structure, gait, finger print, etc [10-14]. Scientists are coming with many new techniques to make robust system for person recognition; imposters are also Imposters are also com-ing with techniques to fool the existing system take advantage of that system. In existing person identification systems, we use Fingerprint is the most widespread biometric, it has been used in forensic for about 100 years. An imposter can fool a finger print system by recreating in latex, similarly can fool the face recognition system by providing photo and can also fool voice recognition by imitating other voice. The possibility to steal data directly from subjects and the relative ease to replicate them (e.g. silicone fingerprints, pictures or facial masks) posed serious challenges to researchers and multimodal recognition systems have been suggested.

# **1.1** Literature survey

In recent years, the Electrocardiogram (ECG) has been proposed as novel biometric for person identification, dedicated research on the ECG analysis has demonstrated its advantages in biometrics: ECG is present in all living individuals, exhibits the typical characteristics of a biometric and it is hard to forge. In addition to this, ECG analysis is a robust method to detect the liveness (the person has to present) characteristic of the subject in authentication scenarios. This special characteristic of ECG helps the system not to be make fool by imposter. ECG is a method to measure and record electrical potential generated by the heart.

The hypothesis of the use of ECG as personal identification attribute was suggested by Scientist Forsen G E[1]; however, the first study on the ECG analysis for biometric purposes was carried out by Biel and colleagues: the authors investigated some combinations of features in 12-leads ECG recordings on a sample of 20 subjects[2][3].

In [8], it is suggested that variability in heart rate could also another measure useful in person identification. ECG data were recorded under several physiological states. To distinguish subjects, the author utilized features including the mean and variance of the R-R interval, along with other ECG parameters such as width of P, R, and T waves. This modality of using ECG data in person identification offers some unique advantages. It is proposed that ECG person identification would be particularly effective in health care applications as the ECG is frequently used to monitor a patient's condition[3],[5]; therefore, without any additional data requirements, this can be used to verify a patient's identity in medical records or other medical procedures.

In [9], ECG data were used as one of source of biometric data along with the facial image data. Supplementing other biometrics with ECG information can be accomplished with little user perceived change in the interface. For example, the ECG data can be recorded simultaneously in fingerprint and

# Fewer cost and superior functioning architecture of VSLI premeditated with Multiplication of Montgomery

Meghana T.M, Pradeep Kumar S K

Meghana T.M PG student/ VLSI and ES, ECE, Kalpataru Institute of Technology Tiptur, Tumkur, India Asst. Prof, Pradeep Kumar S K ECE Department, Kalpataru Institute of Technology Tiptur, Tumkur, India

Abstract - This paper is suggested forth with simple and efficacious Montgomery kind multiplication algorithm such that it is budgetary. Superior performance Montgomery modular multiplier can be enacted in congruence. The suggested multiplier acknowledges and turnouts of the data with the representations of binary utilized one level of Carry skip adder (CSA) to prohibit at the propagation at each summation type operation. This CSA can be premeditated to perform the respective operand at pre -guesstimation and the reformation of format basically from the format of carry save to the binary kind representation, which is following to a cost of low hardware and short cantankerous path lagging at extra clock cycles expense for making a culmination at one multiplication. modular To overcome this particularized weakness, configurable kind CSA could be one full adder or two of the serial half adders, which is suggested forth to lessen especially at the extra clock cycles for the pre-guesstimation operand and the format in reformation by a half. A mechanism is worked to investigate and consider skipping the unnecessary carry save addition operations in the one level CSA (CCSA) type architecture, while managing the short cantankerous path lagging, which has progressed.

Key Words: Carry-save addition, Low-cost architecture, Montgomery modular multiplier, Publickey cryptosystem, Full carry save.

#### **INTRODUCTION**

Modular Multiplication is a cardinal operation in many application areas including public key cryptography [1] .This paper is written with motive at embellishing the performance of the carry skip adder(CSA) based multiplier while managing lesser Montgomery complexity in hardware.[4] Instead of the full carrysave(FCS) based multiplier with two level type CSA architecture semi-carry-save(SCS)based Montgomery modular multiplication(MM) type algorithm and its corresponding hardware in architecture with only one level CSA are suggested forth in this respective paper. Hardware architecture has many benefits and novel contributions over the previous respective designs can be known. First, one level CSA is premeditated forth to perform not only the summation operations in the iteration kind loop of the respective algorithm but also B plus N and the reformation of the format, which is following to a very short cantankerous path and cost being of the low relating to hardware.

First, one level CSA in premeditated to perform summation in the loop of iteration of Montgomery algorithm but also B in addition to N and the reformation of format, following to very short path in cantankerous and lower cost especially at hardware. Anyway, lot of extra clock cycles is essential to carry out B in addition to N and the respective reformation of format via the one level CSA type architecture. Advantage with the short cantankerous path will be lessened. To overcome those weaknesses, we then amend the one-level CSA architecture[3] which is to be able to perform the one three input carry save addition or two serial two input carry save additions,. Hence the extra clock cycles for the respective B in addition to N and the reformation format can be lessened to half. Ultimately, condition and circuit detection, which are basically different with that of the FCS-based multiplier (denoted as FCS MMM42 type multiplier) are progressed to pre-guesstimate quotients and skip those, which are of unnecessary carry save summation operations in the one level configurable CSA type architecture primarily while keeping a short cantankerous path in lagging. Hence, required cycles of clock for culminating one MM operation can be reduced to a greater extent. As the consequence, suggested Montgomery multiplier can be procured higher throughput and the smaller area time product than those of previously discussed Montgomery Multipliers.

# I. MODULAR MULTIPLICATION ALGORITHMS [2]

A. Montgomery type Multiplication

| Algorithm MM:<br>Radix-2 Montgomery modular multiplication |                                                                                                                          |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

|                                                            | Inputs : A, B, N (modulus)<br>Output : S[k]                                                                              |  |

| 2.3.4.                                                     | $S[0] = 0;for i = 0 to k - 1 {q_i = (S[i]_0 + A_i \times B_0) mod 2;S[i+1] = (S[i] + A_i \times B + q_i \times N) / 2;}$ |  |

| 5.<br>6.<br>7.                                             | if $(S[k] \ge N) S[k] = S[k] - N;$<br>return $S[k];$                                                                     |  |

# Link Quality Based Routing for Vertical Handover in Multi Radio Heterogeneous Wireless Mesh Network

<sup>1</sup>G D Gurumurthy, <sup>2</sup>Dr. H S Shivaram, <sup>3</sup>Dr. Mohammad Muazzam

<sup>1</sup>Research Scholar Mewar university Rajasthan, India <sup>2</sup>Research Supervisor Mewar university Rajasthan, India <sup>3</sup>Professor, Mewar University Rajasthan, India

ABSTRACT-Wireless Mesh Network (WMN) an emerging and promising technology in the next generation wireless network offering flexibility in design ,fast deployment, and low cost. WMN are taking advantage of existence of different wireless technologies and their simultaneous availability at a location. Multi mode nodes having multiple radio access interfaces are available to make use of advantages of heterogeneous technologies. Heterogeneous Wireless Networks (HWMN) are the emerging class of Wireless Mesh Network. The routing of the packets in WMN take place through a multi hop path involving Mesh Clients(MC) Mesh Routers(MR), and Internet Gateways(IGW). The routing algorithms suitable for WMN donor perform well for HWMN. These algorithms do not make use of the advantage of heterogeneity in the network. The existing routing protocol need modifications to become suitable for HWMNs and makes use of resources available with heterogeneous networks. The present paper suggests a routing algorithm with is built over AODV algorithm for a HWMN involving Wi-Fi and UMTS network.

**KEYWORDS** -Heterogeneous wireless Mesh Network(HWMN), Multimode nodes, Mesh clients(MC), Mesh routers(MR).

### INTRODUCTION

Mobile networks can be classified as infrastructure based and infrastructure less networks. In infrastructure based network two mobile nodes communicate with each other through a base station and switching system. The base station and switching system control the communication process. Absence of necessity of rigid infrastructure is the feature of infrastructure less networks, mobile nodes can form a network directly and can communicate with each other . Absence of rigid infrastructure make these network a flexible and quickly deployable with low cost [1].Such infrastructure less networks are also called as adhoc networks. Wireless mesh networks are a special class of adhoc networks, which consists of Mesh Clients(MC), Mesh Routers(MR) and Internet Gate Ways(IGW). In the conventional Wi-Fi networks every access point (AP) is connected to the wired network , where as in WMN only a small sub set of APs are connected to the internet through wired network, such APs are called Internet Gate Ways(IGWs) which form the top backbone layer of the wireless mesh network.

The APs that do not have wired connection are called as Mesh Routers (MR). They form the middle back bone layer of the mesh network. Mesh routers communicate with IGW and Mesh clients in wireless mode. The MR forward the traffic towards IGW in a multi hop path.

Mesh Client(MC)are the user mobile devices which form the lower level of the WMN. MCs can make peer to per communication and access internet by establishing a multi hop path involving, MCs MRs and IGW [2].

Mobile nodes have assigned different functions in a WMN. Based on function assumed by mobile nodes the WMN architecture is categorized into: Infrastructure WMNs, Client WMNS, and Heterogeneous WMNs.

Heterogeneous mesh network is a combined feature of infrastructure and client WMN. It supports diverse nodes and interoperability between nodes of heterogeneous technology. The mobile nodes in use are multimode type having interfaces to interact with diverse networks. Heterogeneous WMN offer more flexible design of wireless network taking the advantage of different radio access technologies.

Routing the packets in a WMN is achieved by forwarding the packets among mesh clients nodes and mesh routers following a multi hop path .In homogeneous WMN routing protocols consider that all the nodes in the network have equal capacity and uses common routing metric to find the path quality. In heterogeneous WMN involving multimode nodes and different radio access technologies, it become unrealistic in assuming that all nodes are of equal capacity The routing protocols must take heterogeneity into [3]. consideration. To select a route based on the quality of the links become important. Selecting a route which offer maximum quality which is dependent on various metrics necessitated designing of new route search protocols or the existing route discovery protocols are to be modified to make them suitable for heterogeneous wireless mesh networks.

This paper proposes a modified AODV route discovery protocol which is suitable for o heterogeneous wireless mesh network. The network metric Signal to Noise Ratio(SNR) and Available Bandwidth(AvBw) are used to access the quality of the links between source and destination nodes. The quality of the link is estimated by using a cost function. The links in the path are selected based on the cost offered by the links.

### INTERNATIONAL JOURNAL OF RESEARCH IN ELECTRONICS AND COMPUTER ENGINEERING

# A Novel Canny Mean Restoration Algorithm for Correspondence and Motion Tracking in Dynamic Image Sequence Analysis

G. S. Yogananda Dept of Electronics and Communication Engg. Kalpataru Institute Of Technology, Tiptur

## ABSTRACT

This paper proposes a novel computationally efficient canny mean restoration algorithm for correspondence to identify the matching of the similar features between the reference image frames to the set of search image frames in the dynamic image sequence analysis for tracking motion object in the sequence. This restoration and correspondence has three major steps such as segmentation, feature extraction for restoration, and matching. This paper proposes block-based segmentation in which the reference image frame which contains the object to be tracked can be blocked as square window of size m\*m which covers the object. The next step is the feature extraction for restoration. Here we have considered the block based features in which we calculate the canny edge mean of the region of interest. These features are invariant motion blur and noise of motion deblurring, denioseing and it reduces the dimensionality and finally for matching we made use of the minimum absolute similarity distance measure for these features of the blocks. The searching space is restricted to [-15,+15] pixels in horizontal ,vertical and diagonal directions in the search image frames. The performance of the algorithm is presented for without preprocessed for slow moving objects of various sequences.

#### Keywords

Canny Mean, Restoration, Correspondence, Motion tracking.

#### 1. INTRODUCTION

Image is a 2D function f(x,y) where x & y are planar coordinates. Where x,y & f are discrete image is called as digital image. A digital image consists of fixed number of elements having particular value & location. These elements are called as Pixels or picture elements. Image Restoration is one of the very important techniques in image processing to improve appearance of image. This is done using various techniques like Adaptive filtering, Median filtering etc.

Blurring is one such phenomenon which requires image restoration. Blurring is a kind of Bandwidth reduction of image because of imperfect image formation process. This may result due to relative motion between original image and camera. The blurring process is generalized as convolution of the original image and point spread function(PSF) with additive noise.

#### $g(x, y) = f(x, y) * g(x, y) + \eta$

where g(x, y) is degraded image, f(x,y) is original image g(x,y) is PSF and  $\eta$  is additive noise.

There are many reasons for blurring such as Atmospheric Turbulence, Bad focus, motion between camera and original image. The degrations may be due to sensor motion, blur due Y. P. Gowramma Dept.Of Computer Science & Engg. Kalpataru Institute Of Technology, Tiptur

to cameras focus, relative object camera motion etc. An image can be degraded or corrupted due to various reasons like improper opening of the shutter, atmospheric disturbances, misfocusing etc. Image noise is the random variation of brightness or color information in the image produced by the sensor and circuitry of the scanner and digital camera. Image noise is considered as an undesirable byproduct of image capture. Some types of image noise are Gaussian noise, salt and pepper noise, speckle noise, Brownian noise and many more.

Deconvolution is a long standing problem in many of the application in signal and image processing such as motion pictures (dynamic images), biomedical imaging, astronomy, remote sensing(satellite image processing), super resolution images, forensic images, biometric images and many more. The list is no means exhaustive.

There are many different filter available for deblurring such as mean filter, median filter and adaptive filter which restores images corrupted with noise,

In the motion tracking and correspondence in dynamic scene analysis, image sequence in degraded or blurred due to different types of sequences such as moving object and static sensors, static object & moving sensors, both object & moving sensors.

Tracking or surveillance are important for the security, detecting unlikely events, crime detection in the places like hospitals, schools, corridors, offices, banks, aero drums and many more places. All the sequences undergoes motion, motion undergoes degraded due to many reasons and uncontrolled light sources.

In this research paper we have proposed the canny mean restoration feature correspondence for dynamic scene analysis. Restoration of degraded image sequence for correspondence of dynamic scene analysis is one of the recent hot topics of research in the current trend.

Our research proposes the novel method of restoration for moving image sequence for outdoor image sequence, indoor corridor sequence, face tracking pose change sequence, non rigid body sequence.

## 2. RELATED WORK

Hidetomo Sakanio and Xiqum Lu [25] in 2009 reported a study of spatio temporal derivation sensors to extract both the static edges and the dynamic edges from an input video clip and the static edges refers to those caused by spatial intensity variation while the dynamic edges refers the motion traces of both rigid and non-rigid moving objects in the scenes.

# High-Rapidity and Power-Efficient Carry Skip Adder Performance with AOI and OAI Skip Logic

Amrutavarshini S H<sup>1</sup>, Mr. S Pramod Kumar<sup>2</sup>

<sup>1</sup>PG student/ VLSI and ES, ECE, Kalpataru Institute of Technology Tiptur, Tumkur, India, <sup>2</sup>Asst. Prof, ECE Department, Kalpataru Institute of Technology Tiptur, Tumkur, India

Abstract: In this paper compare to conventional one the new structure of adder contains high speed and uses less energy. The concatenation and the speed and the incrementation scheme can be applied to increase the speed and efficiency of the conventional carry skip adder structure. In CSKA structure the Multiplexer can be used as a skip logic. But in this structure it suggested to replace Multiplexer by the AOI (And Or Invert) OAI (Or And Invert) skip logic. The structure may contain both stages; one is Fixed size stage and another one is Variable size stage. Ultimately Hybrid Variable latency at extension of the suggested structure, which lesses the utilization0f the power without making an impact at the speed which is representing a speed. This extension utilizes amended parallel type structure , basically for segmenting the feeble time thus capaciting at the further reduction of voltage suggested structure are assesed by making a camparision of some parameter that is speed and power with other type of adders utilizing a forty nm static CMOS in technology for a extensive range of supply voltage. Key Words: Carry skip adder(CSKA), Ripple carry adder(RCA), AOI, OAI, Concatenation

# I. INTRODUCTION

In most of the circuits adders are the commonly used unit. Adders are the basic building block in addition, subtraction, multiplication and Memory addressing units. Improving the Adder speed and performance and also reduce the power used is the Main azenda of the designer.

Adders can be differentiated by their speed, power and performance. Some commonly used adders are Ripple carry adder (RCA), Carry select adder (CSLA), Carry skip adder (CSKA), and Parallel prefix adder (PPAs). First considered the RCA; it is the combination of the cascading connection of the Fulladder (FA) in series. Fulladder structure contains some basic gates; it adds two binary digits at any stage of ripple carry adder. Critical path delay is the disadvantage of the Ripple carry adder. In proposed hybrid carry skip adder the parallel prefix adder is the main component used. Different types of PPAs are their; but in this article ,the circuits uses the brunt kung adder. Proposed hybrid CSKA structure can be implemented to reduce the delay and increase the speed and performance.

Proposed hybrid variable CSKA structure can be obtained by the replacing some of the middle stages in CI-CSKA structure with aPPA. Modification is achieved by making use of parallel prefix adder.

## II. CARRY SKIP ADDER

It is one type of adder implementation; it can be used to improve the delay of the Ripple carry adder (RCA) also with small effort compared to other adders. The carry skip adder comes under the category of a by-pass adder and it uses a ripple carry adder for an adder implementation. This adder is an efficient one because of its area and power consumption. CSKA may be implemented using FSS and VSS where the highest speed may be obtained for the VSS structure.

## III. CONVENTIONAL CARRY SKIP ADDER

Conventional carry skip adder contains some of the functional elements like cascading connection of fulladder chains, block of ripple carry adder (RCA), and 2:1 multiplexer. In this structure multiplexer act as a skip logic. RCA blocks are connected each other through this multiplexer. The input of the multiplexer are the carry input of the stage and the carry output of its RCA blocks and the product of propagation signals is bused as a selector signals of the multiplexer. The carry skip adder consider that Ai, Bi are the inputs to the fulladder. The propagate signal Pi is given by

Pi = Ai + Bi where (  $i = 1, 2, 3, \dots, N$ ).

Consider the N bit CSKA it consists of Q stages is given by Q = N/M if carry propagate (cp) equals to the one in a particular stage then cout of that is nothing but cin of the stage.